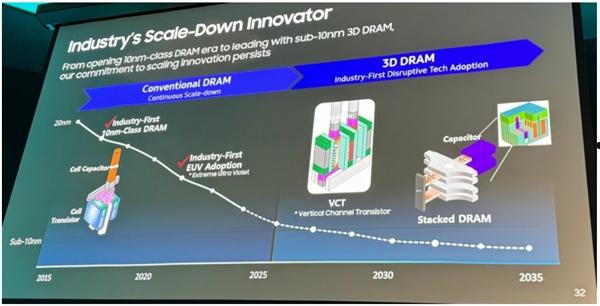

十城科技网4月4日消息,3D晶体管正在各种类型芯片中铺开,3D DRAM内存也讨论了很多年,但一直没有落地。如今三星公开的路线图上,终于出现了3D DRAM。

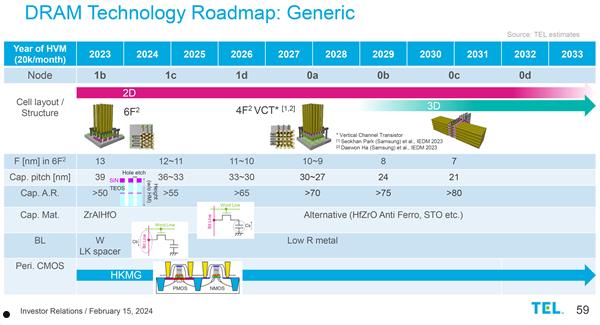

三星的DRAM芯片制造工艺目前处于1b,后续还有1c、1d,都是10nm级别。

再往后的10nm以下节点,将分别命名为0a、0b、0c、0d,其中打头的0a工艺预计2027年底-2028年初量产(月产能超过2万块晶圆),0d则要到2032年。

就在进入10nm之后,三星将全面开启3D内存时代,首先引入VCT(垂直通道晶体管),看起来应该是基础的FinFET类型,而非更先进的GAA。

大约2030-2031年的时候,三星将升级到堆叠DRAM,将多组VCT堆在一起,从而获得更大容量、更高性能,看起来还会引入电容器作为辅助。

发表评论 取消回复